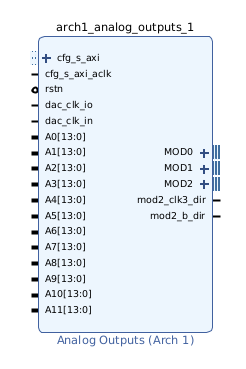

Analog Outputs¶

Control arch 1's analog outputs. This IP and its PYNQ driver depends on other PL peripherals, see Base Design for more information.

Port Description¶

| Port Name | Clock Domain | Description |

|---|---|---|

cfg_s_axi_aclk |

- | Configuration clock |

cfg_s_axi |

cfg_s_axi_aclk |

Configuration AXI interface |

rstn |

cfg_s_axi_aclk |

Active-low reset |

dac_clk_io |

- | Input data clock (5 to 125 MHz) |

dac_clk_in |

- | Must have a +90° phase in relation to dac_clk_io |

data_valid |

dac_clk_io |

Outputs maintain their value when this signal is set to 0 |

A(0..11) |

dac_clk_io |

Input data (signed 14-bit integer) |

MOD0 |

- | Connect to mod0 external port |

MOD1 |

- | Connect to mod1 external port |

MOD2 |

- | Connect to mod2 external port |

mod2_clk3_dir |

- | Connect to mod2_clk3_dir external port |

mod2_b_dir |

- | Connect to mod2_b_dir external port |

PYNQ Driver¶

See the API Reference